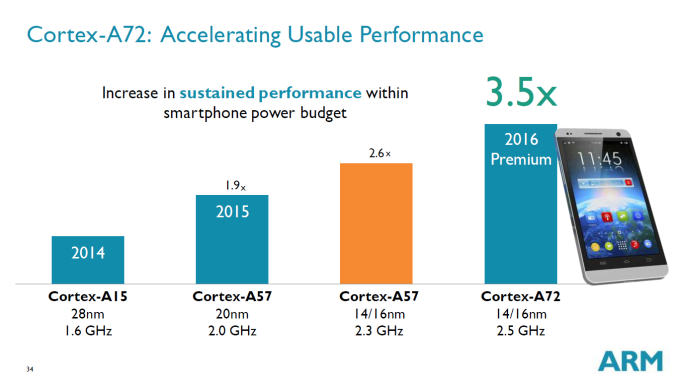

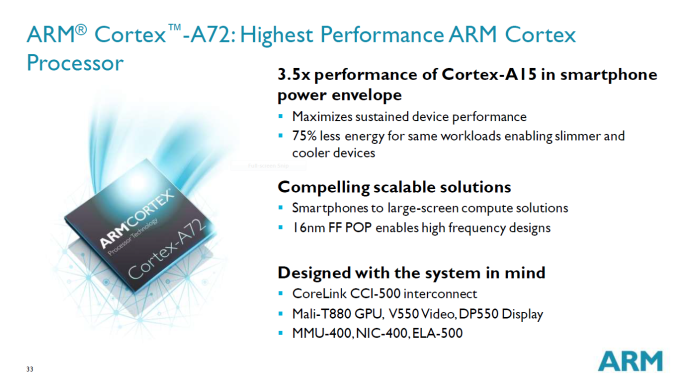

As part of ARM's TechDay 2015 event we had the pleasure to get a better insight into ARM's new Cortex-A72 CPU. ARM had announced the Cortex-A72 in the beginning of February - leaving a lot of questions to be asked and sense of mystery in the air. The Cortex-A72 is a direct successor to the Cortex-A57 - taking the predecessor as a baseline in order to iterate and improve it.

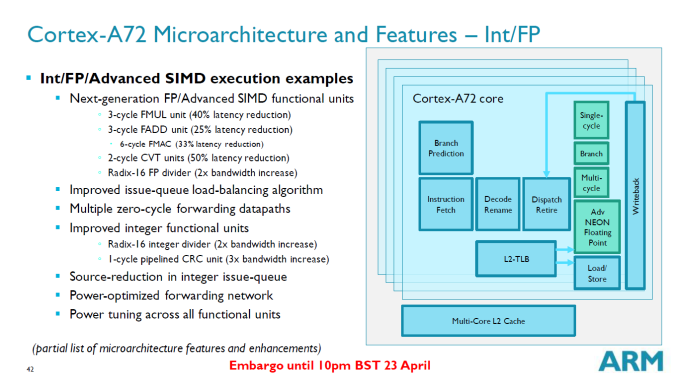

ARM Cortex-A72 offers 20% better branch prediction than its predecessor. Instructions-per-clock have increased between 20% and 60% over the Cortex-A57 depending on the workload. In terms of energy efficiency, the newcomer is between 18% and 30% better than the previous model.

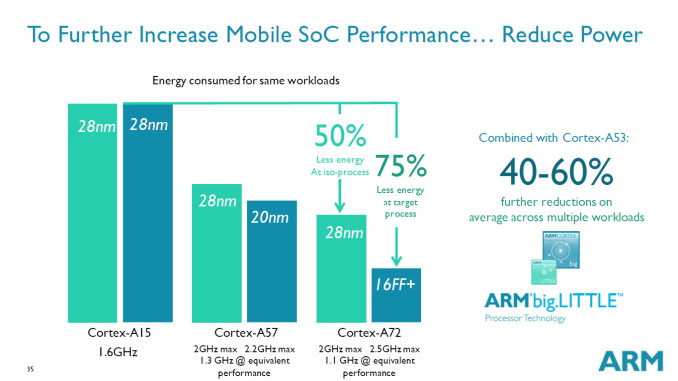

Probably the most interesting slide next to the actual performance metrics of the A72 is the apples-to-apples comparison of the A57 to the A72 on the same process node. When on the 28nm node, we see the A72 having a respectable 20% power reduction when compared to the A57. As a reminder - we're talking about absolute power at the same clock speed, which does not consider performance and thus not a representation of efficiency.

| ARM CPU Core Comparison | ||||||

| Cortex-A15 | Cortex-A57 | Cortex-A72 | ||||

| ARM ISA | ARMv7 (32-bit) | ARMv8 (32/64-bit) | ||||

| Decoder Width | 3 ops | |||||

| Maximum Pipeline Length | 19 stages | 16 stages | ||||

| Integer Pipeline Length | 14 stages | |||||

| Branch Mispredict Penalty | 15 cycles | |||||

| Integer Add | 2 | |||||

| Integer Mul | 1 | |||||

| Load/Store Units | 1 + 1 (Dedicated L/S) | |||||

| Branch Units | 1 | |||||

| FP/NEON ALUs | 2x64-bit | 2x128-bit | ||||

| L1 Cache | 32KB I$ + 32KB D$ | 48KB I$ + 32KB D$ | ||||

| L2 Cache | 512KB - 4MB | 512KB - 2MB | 512KB - 4MB | |||

Slides courtesy of AnandTech

Another large performance improvement over the A57 is found on the Load/Store unit. Here, ARM claims that bandwidth to L1/L2 has been improved by up to 30%. This was achieved by introducing a sophisticated L1/L2 data prefetcher which, again, is at the same time more efficient as improvements in the L1-hit pipeline, forwarding network, and way-predictor reduce the needed power.The A72 looks to be a logical update to the A57 addressing some weakpoints such as peak power and power efficiency combined with an ~10% area reduction. We already saw Mediatek showing off an A72 package at MWC, so it will be interesting to see how the IP actually performs in silicon and what ARM's partners will be able to do with the core and the time to market.